|

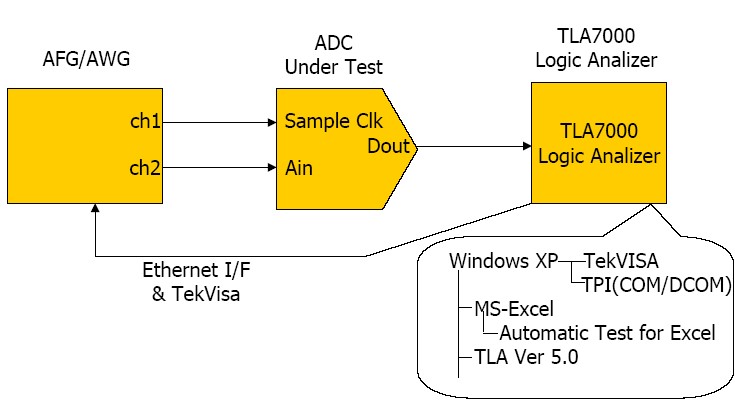

ADC��DAC�yԇ����̩��ᘌ���·����ADC��DAC�Ĝyԇ����̩���ṩ��ADC����:ᘌ�������ߵĸ���ADCϵ�y�Ĝyԇ�ͼ��̩�ˌ��Tᘌ�ADC�yԇ����C�ď��s�ԣ�ͨ�^TLA7000߉�����x��ʾ�����o�p���ɣ��ṩ��2�������ADC�yԇ�ͷ������ܡ� ADC�����Ĝyԇ�����c��Ҫ������CADC�D�Q�^���еĸ��N�ӑB���o�B���ԣ����w�܉�ͨ�^̩��TLA߉�����x��DPO71254C���֟ɹ�ʾ�����܉��ṩ�Ĝyԇ�������£� SNR ENOB SINAD THD SFDR Jitter test and analysis ADC Transient Response ADC Over-voltage Recovery Time ����ADCģ�Mݔ���time skew �^������o�B���� Logic Input Logic Output Clock Period Clock Pulse-width High Clock Pulse-width Low Output Delay ����ADC��߉ݔ��time skew�yԇ �D��ADC�Ĝyԇ�h����

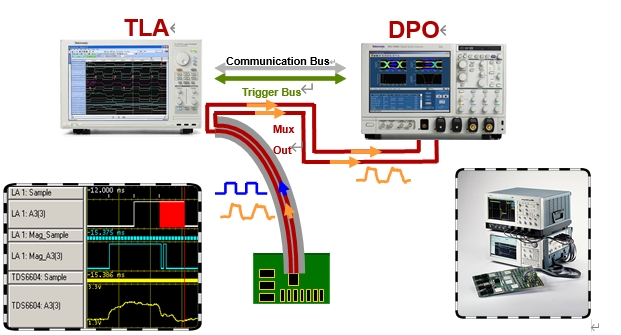

ݔ����̖�a������̖�{�����ֵ���C��ADC�Ĝyԇ��Ҫ�߾���ֱ��늉�Դ���c�lԴ�͌���ʸ���{��Դ��ֱ��Դ���c�lԴ���齛��Ĝyԇ���ߟo���Mһ���U��������ǰ�ĸ���ADCϵ�y���f��խ��/ֱ����̖��푑���������ȫ���������ܣ�����߀��Ҫ�o���䌦������̖��푑����ԣ����Ԍ���/������ʸ���{��ԴҲ����ADCϵ�y�Ĝyԇ��ʹ�õ���̩��AWG70002��һ�N���͵�һ�w��������ʸ���{����̖Դ�����IJɘ��ʿ����_��25GS/s����ߵ��{�Ǝ����ɳ��^10GHz��ʹ�ú��㣬�^���m�ϸ���ADC�Č������ ��һ���棬����ADCϵ�y����������̖�{���·���r��·���ɘӱ����·���D�Q�·�Ȳ��֣�ÿһ���ֶ�������K�D���Y���a��Ӱ푡���ADCϵ�y���аl�A�Σ����˸��x��ͬ���ֵ�Ӱ푣���Ҫʹ�Üyԇ�O�䌦�@Щ���ֵ�ݔ���M�Мyԇ�����õĹ��߰���늉������f�ñ�����ʾ�������l�V�����x��������ͬ�ļ�����̖�x��ͬ�Ĝyԇ�O�䣬��ֱ���������늉���y�����r�/խ��/�������l��������l�V�����x������������̖����ʹ���l�V�x�^�y�l�V���⣬߀��Ҫʹ��ʾ�����@�N���������ՙC�M��ʸ�����{��C��̩�˹�˾���@���涼���^�����Ľ�Q����������DMM4050��λ�딵���f�ñ���RSA5106A���r�l�V�����x��DPO70000Cϵ�Д��֟ɹ�ʾ�������SignalVuʸ����̖����ܛ���M�ɵij�����ʸ����̖����ϵ�y�� ADCϵ�y����C���{ԇ�����c��Ҫ���ڌ���ʹ��ADC�D�Q�Ĕ����M����C������ͬ�rͨ�^̩���ṩ��iLink���߰���ÿһ��ADC��̖�ṩ��̖�����ԵĜyԇ�ͷ����� ����һ������ADC�ɘӣ��M���M�Д���������̎����ϵ�y����Ҫ�߾��ȵĕr�g����̖�����Ԝyԇ����ϵ�y���ڕr犷��䣬�r犺͔���PCB�������Լ�ADC�����Ć��}�r����Ҫ���m�Ĝyԇ���ߌ�����ԭ���M�ж�λ�ͷ����� ̩��TLA߉�����x��DPOʾ�����M��ϵ�y�������M������ADC�����yԇ�⣬ᘌ��OӋ��ʹ�ø���ADC��ϵ�y�ṩ�ṩȫ��Ĝyԇ���{ԇ���ܡ��������ADC���^50M����ݔ����̖����Էdz��P�I��TLA��DPO���Ծ��_��ݵİl�F���N��̖�����Ԇ��}�Ϳ������φ��}��ͬ�r�ṩ���r���̖�ķ���r�ӺͶ����ṩȫ��Ĝyԇ�ͷ��������� �D��̩��ʾ������߉�����x�M�ɵĜyԇϵ�y��D��

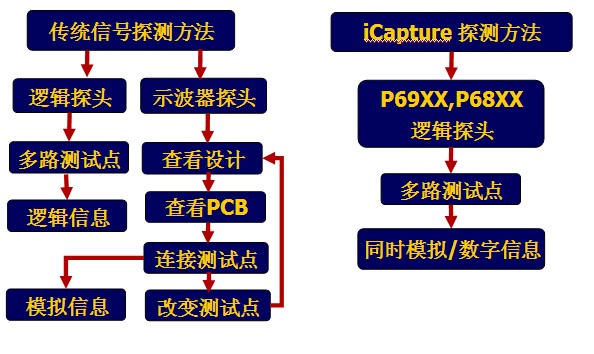

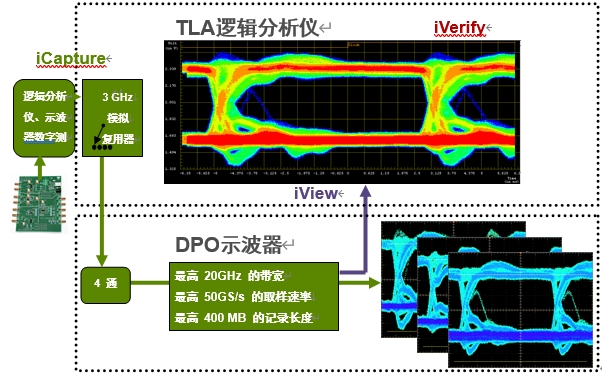

ԓϵ�y��Ҫ�ṩ�Ĺ��ܷQ�� iLink���߰����������˃ɷN���ߵ����c����DPO���֟ɹ�ʾ�������M�㱻�yϵ�yģ�M��������Ҫ���B�ӵ�߉�����x��ͨ�^��ģ�M��͔�����Ĺ������������ṩ�I��Ψһ��iCapture̽�^��ԓ̽�^�܉��^�yADC������ģ�M������Ϣ��ͬ�r�^����ͬ��̖�Ĕ��ִa����Ϣ���@���M��ȫ�����̖�����Է�������÷�����߉�����x�ȿ��@ʾ������Ϣ�����ܕr�g���P���@ʾԓ������ģ�M���Σ��OӋ�ˆT�Ϳ��Ԍ�������̖��ģ�M�����M���^�죬�ų�ϵ�y�е��e�`�� ADCݔ����̖�Ĝyԇ�B�� �����M��ADC֮�g�ĵ�ݔ�������ĕr�gƫ��yԇ���Լ�����ÿһ��ADC �Ĕ���ƫ��yԇ��������Ҫ���]���Ƕ�ͨ���Ĝyԇ�B�ӡ� ���˱��C��ADC��̖��̽�y���B�ӣ���TLA7000ϵ��߉�����x��̽�^ǰ�˲�����Դ�N�����·��ÿһ��̽�^��ݔ������ؓ�d��0.5pf�������ṩ3GHz���ϵ�ģ�M������ԓ̽�^�ɞ�iCapture̽�^������iCapture���g����Դ߉̽�^������ģ�M������3GHz���܉�ֱ���ڜyԇ�^����ͨ�^ʾ������ρ�ֱ�ӌ�ADC����ݔ����̖��ģ�M������Ϣ�M���^�y���o����ʹ��ʾ������̽�^�ڱ��y�·���ό��Ҝyԇ�c���؏�̽�y���@��������ϵ�y��ֻʹ��һ��̽�^���܉����߉��ģ�M�Ĝyԇ������̽�^��ݔ����ݞ�0.5pf�����C�����yϵ�yӰ���С�� ���B�ӷ�ʽ�ϣ�߉�����x̽�^�ͱ��y�·���B�Ӳ��É��ӵķ�ʽ�����o����y�Ğ�߉�����x̽�^�yԇ�ṩ�Ĝyԇ�������B���������̎����M�пɜy���OӋ�r��ֻ��Ҫ����̽�^ָ�����ṩ�ęCе�ߴ磬��Ԫ�������OӋ���֜yԇ���P��PCB���ϼ��ɡ��@�N�o�B������ʽ��߉̽�^�B�ӿ��Ա��CPCB�����yԇ�c�r�a���Ě����M���ܵ�С�����ҜpС���M�пɜy���OӋ�r�IJ������s�ȣ�ͬ�r�������̖�����ԡ��D��̩��iCapture̽�y�����͂��y̽�y�����Č��ȡ�

ADCݔ����̖����̖�����Ԝyԇ�͕r�gƫ��yԇ����Ҫ����ADC��ݔ�������r�gƫ��}�r������ʹ��TLA7000߉�����x�ṩ��iVerify�ۈD�yԇ���ܣ������M��128��������̖���ۈD�yԇ���ص�����̖�����Ԇ��}���� ADC����ݔ���У�ÿһ·�Ĕ����͕r犵��Pϵͨ�^�ۈD�@ʾ�������@�Ӿ��܉��M�Еr�gƫ�����̖�����Եķ��������D��ʾ��

ADCϵ�y�Еr犺͔�����̖�Ķ��Ӝyԇ�͕r�gƫ��yԇ ����ݔ����̖ͨ�^ADC�D�Q�锵����̖���Լ��M�Д���̎�����^���У��r�Դ�������λ�Ͷ��ӷdz���Ҫ��̩��ʾ�������DPOJET�����Ӻ͕r�g�yԇܛ���ṩ�����¹��ܣ� �r状��ӵĜyԇ�ͷ��� �r���λ���ӵĜyԇ�ͷ��� �r犣������r�gƫ��Ĝyԇ �r犣��r犕r�gƫ��Ĝyԇ �����������r�gƫ��Ĝyԇ ̩�����]������: 1�_TLA7012���C��TLA7BB4��������߉�����xģ�K��64M�����ɼ��ȴ��x�� 4��P6960��P6980߉�����x̽�^������ֱ�����ʾ����ʹ�ã��ṩ3GHZģ�M������ 1�_DPO71254C���֟ɹ�ʾ���� �����r�Ͷ��ӷ���ܛ��DPOJET ��ʸ����̖����ܛ��SignalVu ���r�l�V�����xRSA5106A �����f�ñ� DMM4050

̩���ṩ��DAC����1��DAC�Ĝyԇ��ʹ����Ҫ�������ṩ��D�ˡ��ļ�����̖�͡�A����ݔ����̖�ķ�������Ҫ��Ҫ�������Ŀ�У� ���N�o�B���� ���N�ӑB��������Ҫ������ ݔ���������ʣ������l�ʣ� ���V�ܶ� SFDR ACLR ݔ������ ģ�Mݔ����������Ҫ���� ݔ���������½��r�g ݔ���ӕr ��Cݔ����̖��������Ҫ���� ݔ�딵�����r���̖�Ľ���/���֕r�g ������l�� �r���/ؓռ�ձ����� ݔ����̖�ƽ��������

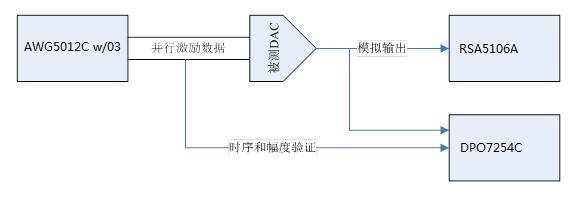

̩�˹�˾�ṩ�Ĝyԇ�����������Ⲩ�ΰl����AWG5012C�͌��r�l�V�����xRSA5106A�����֟ɹ�ʾ����DPO71254C���yԇԭ����D���£�

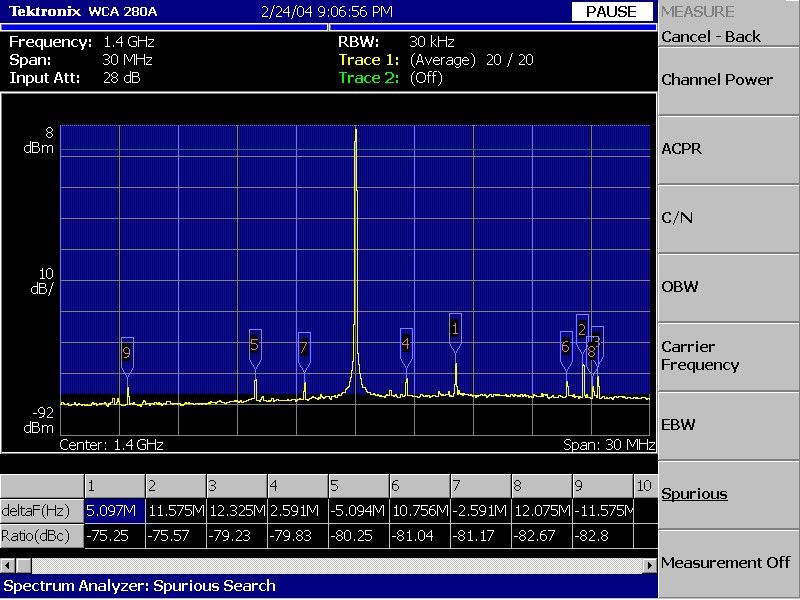

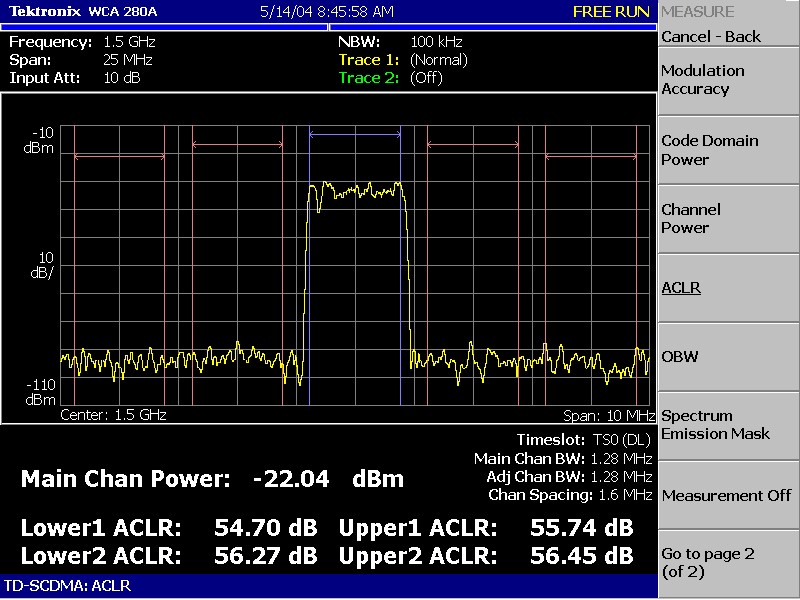

2����ADC�yԇ��ƣ�DAC�yԇ��һ���P�I�c����CDACݔ��ָ�ˣ��˕rRSA5106A���r�l�V�����x���Ԝyԇ�l��ָ�ˣ����sɢ��SFDR�ȣ�ͬ�rDPO71254C���Ԝyԇ���P�r��ָ�ˣ�������/�½��r�g�ȡ� RSA5106A��һ��������Σ��yԇʮ�ַ�����l�V�x�����Կ��ٵõ����N�l��ָ�ˣ����D��ʾ���sɢ�y����ͨ�^�Ԅӵ��sɢ�yӋ�б����Ñ����������õ�SFDR�Ȝyԇ�Y����

ͬ�ӣ��D��һ��ACLR�ԄӜyԇ������

3��DAC�yԇ�е���һ�������ǔ�����̖���AWG5012C w/03�����ṩ��������_1200M��λ����32bit��ͬ�������֞�16·������Ҫ�����飺 ͨ������32·�ζ˻�16·��֔���ͨ���� ���ʣ�10M~1200Mbps �����r�g�� <300ps ÿͨ��������ȣ�16Mλ ݔ�����ȣ� 0.1~3.7Vpp��50�Wķ��0.2~7.4Vpp��1M�Wķ���ֱ��ʞ�10mV ͨ���g�r�ӣ�<400ps �ڜyԇ�У�AWG5012Cϵ�y���H����ݔ������ļ�����̖��yԇDAC�ӑB������߀���Ը�׃ݔ�������Լ�ͨ���gͬ����r�ȁ���CDAC��ݔ����̖���Ⱥ͕r�����ޣ� 4������һЩ�r��ָ�ˣ�������/�½��r�g������ʹ��ʾ����DPO71254C��DPO71254C߀��������AWG������̖����C�����ڜyԇ�ӑB������֮ǰ������ʾ�����^��AWGݔ������̖�Ƿ��ѽ����_���á� 5�����]���� AWG5012C ��03�x� RSA5106A���r�l�V�����x DPO71254C���֟ɹ�ʾ���� |