ADC和DAC測(cè)試方案

泰克針對(duì)多路高速ADC和DAC的測(cè)試方案

泰克提供的ADC方案:

針對(duì)日益提高的高速ADC系統(tǒng)的測(cè)試和激勵(lì),泰克專門針對(duì)ADC測(cè)試和驗(yàn)證的復(fù)雜性,通過TLA7000邏輯分析儀和示波器無縫集成,提供了2個(gè)層面的ADC測(cè)試和分析功能。

ADC參數(shù)的測(cè)試,重點(diǎn)主要在于驗(yàn)證ADC轉(zhuǎn)換過程中的各種動(dòng)態(tài)和靜態(tài)特性,具體能夠通過泰克TLA邏輯分析儀和DPO71254C數(shù)字熒光示波器能夠提供的測(cè)試參數(shù)如下:

SNR

ENOB

SINAD

THD

SFDR

Jitter test and analysis

ADC Transient Response

ADC Over-voltage Recovery Time

多個(gè)ADC模擬輸入的time skew

絕大多數(shù)靜態(tài)參數(shù)

Logic Input

Logic Output

Clock Period

Clock Pulse-width High

Clock Pulse-width Low

Output Delay

多個(gè)ADC的邏輯輸出time skew測(cè)試

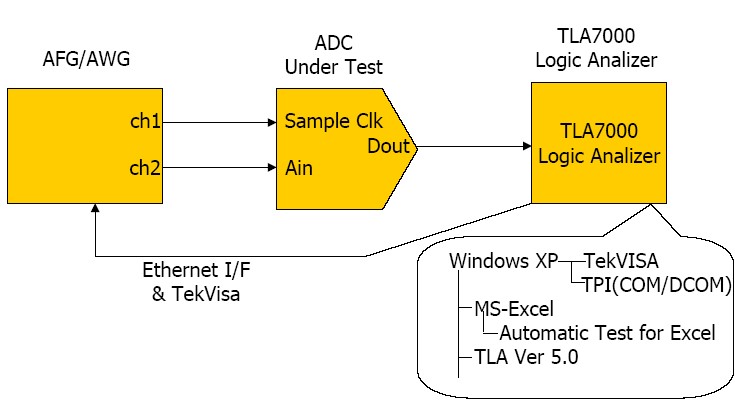

下圖是ADC的測(cè)試環(huán)境:

輸入信號(hào)產(chǎn)生和信號(hào)調(diào)理部分的驗(yàn)證。ADC的測(cè)試需要高精度直流電壓源,點(diǎn)頻源和寬帶矢量調(diào)制源。直流源和點(diǎn)頻源作為經(jīng)典的測(cè)試工具無需進(jìn)一步闡述,對(duì)當(dāng)前的高速ADC系統(tǒng)來說,窄帶/直流信號(hào)的響應(yīng)并不能完全表征其性能,常常還需要給出其對(duì)寬帶信號(hào)的響應(yīng)特性,所以寬帶/超寬帶矢量調(diào)制源也會(huì)在ADC系統(tǒng)的測(cè)試中使用到。泰克AWG70002是一種典型的一體化超寬帶矢量調(diào)制信號(hào)源,它的采樣率可以達(dá)到25GS/s,最高的調(diào)制帶寬可超過10GHz,使用簡便,較為適合高速ADC的寬帶激勵(lì)。

另一方面,高速ADC系統(tǒng)常常包括信號(hào)調(diào)理電路、時(shí)鐘電路、采樣保持電路和轉(zhuǎn)換電路等部分,每一部分都會(huì)對(duì)最終轉(zhuǎn)化結(jié)果產(chǎn)生影響。在ADC系統(tǒng)的研發(fā)階段,為了隔離不同部分的影響,需要使用測(cè)試設(shè)備對(duì)這些部分的輸出進(jìn)行測(cè)試,常用的工具包括電壓表(萬用表)、示波器和頻譜分析儀,根據(jù)不同的激勵(lì)信號(hào)選擇不同的測(cè)試設(shè)備,如直流激勵(lì)可用電壓表測(cè)量;時(shí)鐘/窄帶/寬帶射頻激勵(lì)可用頻譜分析儀;而超寬帶信號(hào)除了使用頻譜儀觀測(cè)頻譜以外,還需要使用示波器這種超寬帶接收機(jī)進(jìn)行矢量解調(diào)驗(yàn)證。泰克公司在這方面都有較為完備的解決方案,包括DMM4050六位半數(shù)字萬用表,RSA5106A實(shí)時(shí)頻譜分析儀和DPO70000C系列數(shù)字熒光示波器配合SignalVu矢量信號(hào)分析軟件組成的超寬帶矢量信號(hào)分析系統(tǒng)。

ADC系統(tǒng)的驗(yàn)證和調(diào)試,重點(diǎn)主要在于對(duì)于使用ADC轉(zhuǎn)換的數(shù)據(jù)進(jìn)行驗(yàn)證分析;同時(shí)通過泰克提供的iLink工具包對(duì)每一個(gè)ADC信號(hào)提供信號(hào)完整性的測(cè)試和分析。

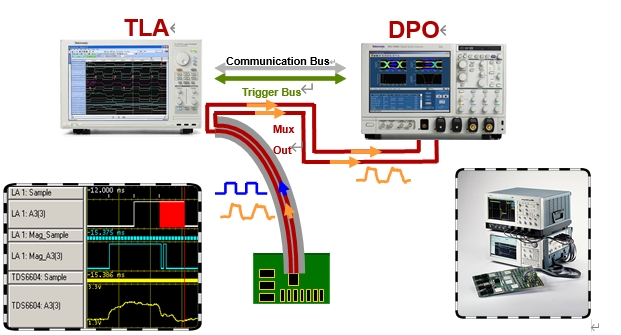

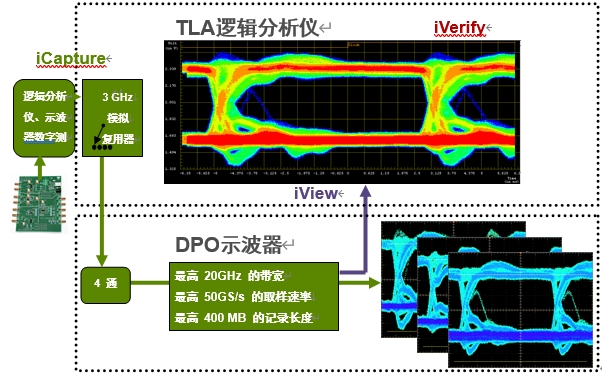

作為一個(gè)高速ADC采樣,進(jìn)而進(jìn)行數(shù)據(jù)分析和處理的系統(tǒng),需要高精度的時(shí)間和信號(hào)完整性測(cè)試。當(dāng)系統(tǒng)由于時(shí)鐘分配,時(shí)鐘和數(shù)據(jù)PCB布線,以及ADC自身的問題時(shí),需要合適的測(cè)試工具對(duì)故障原因進(jìn)行定位和分析。 泰克TLA邏輯分析儀和DPO示波器組成系統(tǒng),除了進(jìn)行上述ADC參數(shù)測(cè)試外,針對(duì)設(shè)計(jì)中使用高速ADC的系統(tǒng)提供提供全面的測(cè)試和調(diào)試功能。例如高速ADC超過50M后,數(shù)字輸出信號(hào)電特性非常關(guān)鍵,TLA和DPO可以精確快捷的發(fā)現(xiàn)各種信號(hào)完整性問題和總線故障問題,同時(shí)提供對(duì)時(shí)鐘信號(hào)的分配時(shí)延和抖動(dòng)提供全面的測(cè)試和分析方案。 下圖是泰克示波器和邏輯分析儀組成的測(cè)試系統(tǒng)框圖。

該系統(tǒng)主要提供的功能稱為 iLink工具包。它集成了兩種工具的特點(diǎn),將DPO數(shù)字熒光示波器(滿足被測(cè)系統(tǒng)模擬帶寬的需要)連接到邏輯分析儀。通過將模擬域和數(shù)據(jù)域的工具聯(lián)合起來,提供業(yè)內(nèi)唯一的iCapture探頭,該探頭能夠觀測(cè)ADC數(shù)據(jù)的模擬參數(shù)信息的同時(shí)觀察相同信號(hào)的數(shù)字碼流信息,這是進(jìn)行全面的信號(hào)完整性分析的最好方法。邏輯分析儀既可顯示數(shù)字信息,又能時(shí)間相關(guān)的顯示該數(shù)據(jù)的模擬波形,設(shè)計(jì)人員就可以對(duì)數(shù)字信號(hào)的模擬特性進(jìn)行觀察,排除系統(tǒng)中的錯(cuò)誤。

ADC輸出信號(hào)的測(cè)試連接

對(duì)于進(jìn)行ADC之間的的輸出數(shù)據(jù)的時(shí)間偏差測(cè)試;以及對(duì)于每一個(gè)ADC 的數(shù)據(jù)偏差測(cè)試,首先需要考慮的是多通道的測(cè)試連接。

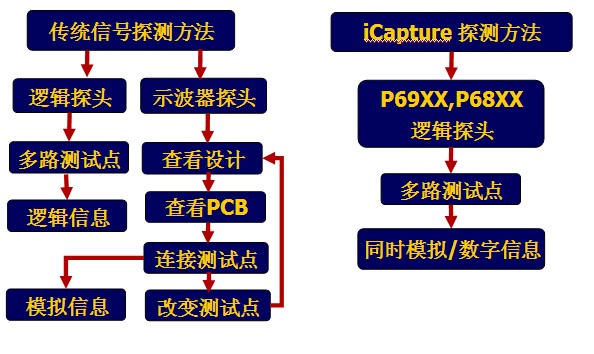

為了保證對(duì)ADC信號(hào)的探測(cè)和連接,在TLA7000系列邏輯分析儀的探頭前端采用有源鍺化硅電路,每一個(gè)探頭的輸入容性負(fù)載為0.5pf,并且提供3GHz以上的模擬帶寬,該探頭成為iCapture探頭。采用iCapture技術(shù)的有源邏輯探頭,它的模擬帶寬為3GHz,能夠直接在測(cè)試過程中通過示波器配合來直接對(duì)ADC數(shù)字輸出信號(hào)的模擬參數(shù)信息進(jìn)行觀測(cè),無需在使用示波器的探頭在被測(cè)電路板上尋找測(cè)試點(diǎn)來重復(fù)探測(cè)。這樣在整個(gè)系統(tǒng)在只使用一套探頭就能夠完成邏輯和模擬的測(cè)試,整個(gè)探頭的輸入電容為0.5pf,保證對(duì)被測(cè)系統(tǒng)影響最小。

在連接方式上,邏輯分析儀探頭和被測(cè)電路的連接采用壓接的方式,即無需傳統(tǒng)的為邏輯分析儀探頭測(cè)試提供的測(cè)試插座或連接器。工程師在進(jìn)行可測(cè)性設(shè)計(jì)時(shí),只需要按照探頭指南所提供的機(jī)械尺寸,在元件庫中設(shè)計(jì)部分測(cè)試焊盤在PCB板上即可。這種無連接器方式的邏輯探頭連接可以保證PCB布線測(cè)試點(diǎn)時(shí)產(chǎn)生的殘樁盡可能的小,并且減小了進(jìn)行可測(cè)性設(shè)計(jì)時(shí)的布線復(fù)雜度,同時(shí)提高了信號(hào)完整性。下圖是泰克iCapture探測(cè)方法和傳統(tǒng)探測(cè)方法的對(duì)比。

ADC輸出信號(hào)的信號(hào)完整性測(cè)試和時(shí)間偏差測(cè)試當(dāng)需要分析ADC的輸出數(shù)據(jù)時(shí)間偏差問題時(shí),可以使用TLA7000邏輯分析儀提供的iVerify眼圖測(cè)試功能,可以進(jìn)行128個(gè)高速信號(hào)的眼圖測(cè)試,徹底分析信號(hào)完整性問題。在 ADC數(shù)據(jù)輸出中,每一路的數(shù)據(jù)和時(shí)鐘的關(guān)系通過眼圖顯示出來,這樣就能夠進(jìn)行時(shí)間偏差和信號(hào)完整性的分析。如下圖所示。

ADC系統(tǒng)中時(shí)鐘和數(shù)據(jù)信號(hào)的抖動(dòng)測(cè)試和時(shí)間偏差測(cè)試

由于輸入信號(hào)通過ADC轉(zhuǎn)換為數(shù)字信號(hào),以及進(jìn)行數(shù)字處理的過程中,時(shí)鐘源分配的相位和抖動(dòng)非常重要。泰克示波器配合DPOJET高級(jí)抖動(dòng)和時(shí)間測(cè)試軟件提供了如下功能:

時(shí)鐘抖動(dòng)的測(cè)試和分析

時(shí)鐘相位抖動(dòng)的測(cè)試和分析

時(shí)鐘-數(shù)據(jù)時(shí)間偏差的測(cè)試

時(shí)鐘-時(shí)鐘時(shí)間偏差的測(cè)試

數(shù)據(jù)-數(shù)據(jù)時(shí)間偏差的測(cè)試

泰克推薦的配置:

1臺(tái)TLA7012主機(jī)配TLA7BB4超高性能邏輯分析儀模塊,64M獨(dú)立采集內(nèi)存選件

4個(gè)P6960或P6980邏輯分析儀探頭(可以直接配合示波器使用,提供3GHZ模擬帶寬)

1臺(tái)DPO71254C數(shù)字熒光示波器

高級(jí)定時(shí)和抖動(dòng)分析軟件DPOJET

高級(jí)矢量信號(hào)分析軟件SignalVu

實(shí)時(shí)頻譜分析儀RSA5106A

數(shù)字萬用表 DMM4050

泰克提供的DAC方案

1、DAC的測(cè)試,使用主要工具是提供“D端”的激勵(lì)信號(hào)和“A”端輸出信號(hào)的分析。主要需要分析的項(xiàng)目有:

各種靜態(tài)參數(shù)

各種動(dòng)態(tài)參數(shù),主要包括:

輸出更新速率(工作頻率)

噪聲譜密度

SFDR

ACLR

輸出帶寬

模擬輸出參數(shù),主要包括

輸出上升、下降時(shí)間

輸出延時(shí)

驗(yàn)證輸入信號(hào)能力,主要包括

輸入數(shù)據(jù)對(duì)時(shí)鐘信號(hào)的建立/保持時(shí)間

最大工作頻率

時(shí)鐘正/負(fù)占空比限制

輸入信號(hào)電平幅度限制

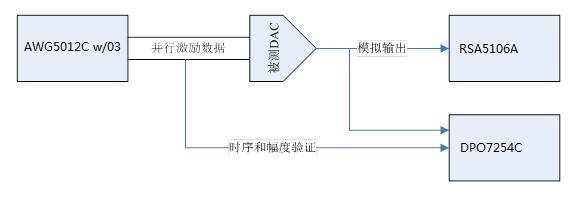

泰克公司提供的測(cè)試方案包括任意波形發(fā)生器AWG5012C和實(shí)時(shí)頻譜分析儀RSA5106A,數(shù)字熒光示波器DPO71254C,測(cè)試原理框圖如下:

2、和ADC測(cè)試類似,DAC測(cè)試的一個(gè)關(guān)鍵點(diǎn)是驗(yàn)證DAC輸出指標(biāo),此時(shí)RSA5106A實(shí)時(shí)頻譜分析儀可以測(cè)試頻域指標(biāo),如雜散、SFDR等,同時(shí)DPO71254C可以測(cè)試相關(guān)時(shí)域指標(biāo),如上升/下降時(shí)間等。

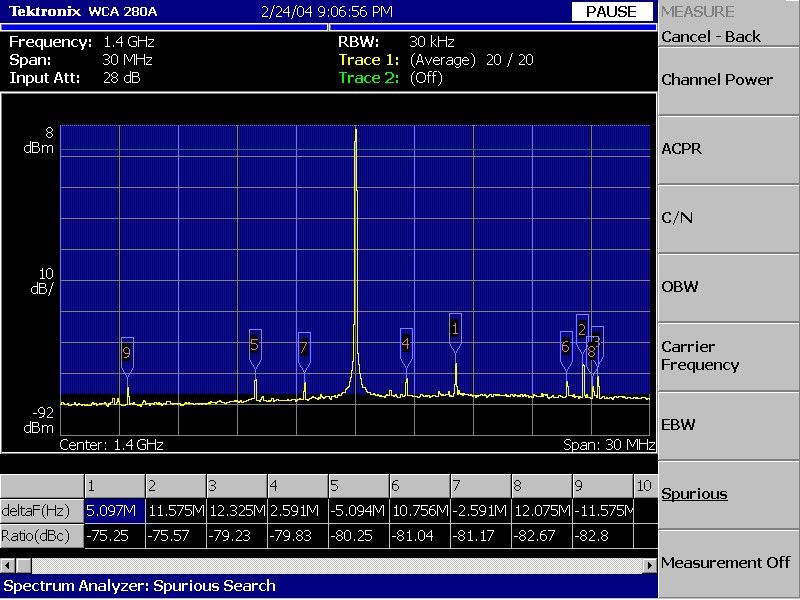

RSA5106A是一款操作簡單,測(cè)試十分方便的頻譜儀,可以快速得到各種頻域指標(biāo),如下圖所示的雜散測(cè)量。通過自動(dòng)的雜散統(tǒng)計(jì)列表,用戶可以立即得到SFDR等測(cè)試結(jié)果:

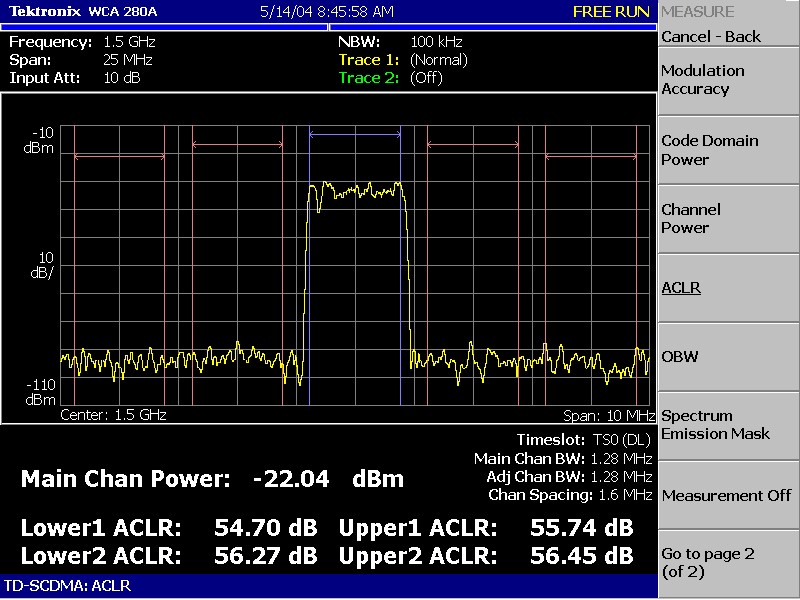

同樣,下圖是一個(gè)ACLR自動(dòng)測(cè)試的例子

3、DAC測(cè)試中的另一個(gè)工具是數(shù)字信號(hào)激勵(lì)。AWG5012C w/03可以提供速率最高達(dá)1200M,位寬為32bit的同步激勵(lì)(差分為16路)。主要參數(shù)為:

通道數(shù):32路單端或16路差分?jǐn)?shù)據(jù)通道;

速率:10M~1200Mbps

上升時(shí)間: <300ps

每通道數(shù)據(jù)深度:16M位

輸出幅度: 0.1~3.7Vpp至50歐姆,0.2~7.4Vpp至1M歐姆,分辨率為10mV

通道間時(shí)延:<400ps

在測(cè)試中,AWG5012C系統(tǒng)不僅可以輸出理想的激勵(lì)信號(hào)來測(cè)試DAC動(dòng)態(tài)參數(shù),還可以改變輸出幅度以及通道間同步情況等來驗(yàn)證DAC的輸入信號(hào)幅度和時(shí)序容限;

4、其它一些時(shí)域指標(biāo),如上升/下降時(shí)間,可以使用示波器DPO71254C。DPO71254C還可以用于AWG激勵(lì)信號(hào)的驗(yàn)證,即在測(cè)試動(dòng)態(tài)參數(shù)等之前,先用示波器觀察AWG輸出的信號(hào)是否已經(jīng)正確配置。

5、推薦配置

AWG5012C 帶03選項(xiàng)

RSA5106A實(shí)時(shí)頻譜分析儀

DPO71254C數(shù)字熒光示波器

推荐

-

-

QQ空间

-

新浪微博

-

人人网

-

豆瓣